Logic family generator¶

logic

logic

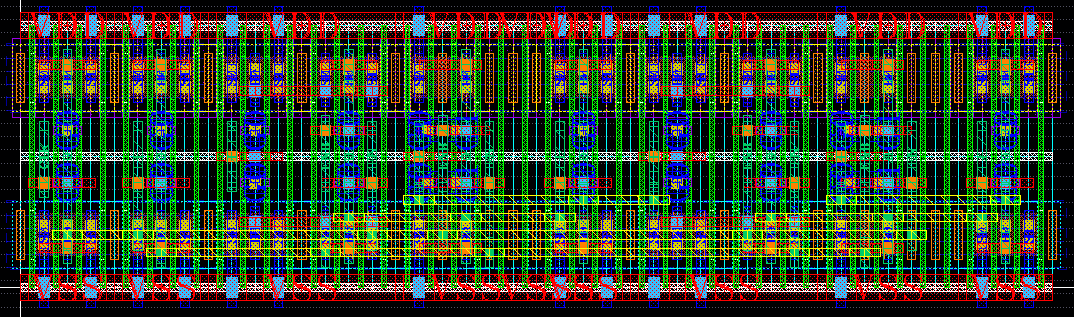

This section describes how to generate logic gate layout templates, which are used for constructing custom digital cells.

Note: the codes are lengthy and not cleaned up yet. An improved version following the tutorial conventions (possibly with more abstracting functions) will be released soon.

Install and launch¶

Clone a proper tech repo. For cds_ff_mpt example type following commands.

$ git clone git@github.com:ucb-art/BAG2_cds_ff_mpt.git $ cd BAG2_cds_ff_mpt $ git submodule init $ git submodule update $ git submodule foreach git pull origin master

Set setting up files, run virtuoso and BAG.

Run this command to generate logic layouts. The script will create logic layouts in (tech)_logic_templates library. For example, for cds_ff_mpt technology, the library name will be cds_ff_mpt_logic_template.

run laygo/generators/logic/logic_templates_layout_generator.py

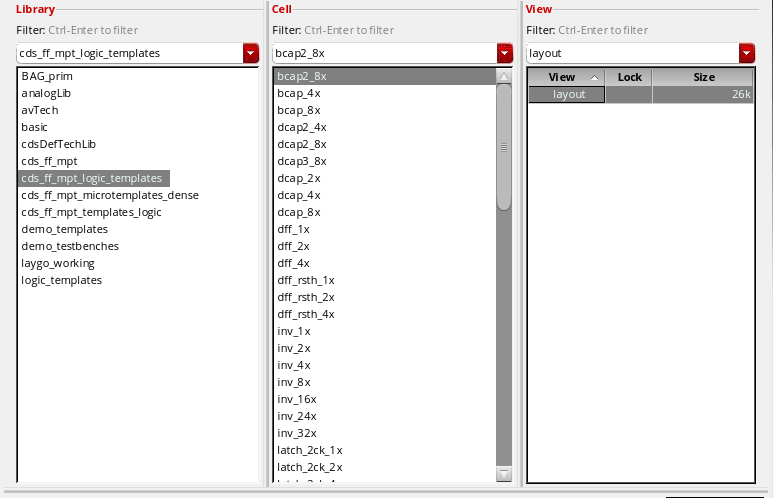

Open (tech)_logic_templates library and check if cells are generated.

logic_lib

logic_lib

Supported logic gate types¶

- bcap : capacitors

- dcap : decoupling capacitors

- dff : D flip-flops

- dff_rsth : D flip-flops with reset high

- inv : inverters

- latch_2ck : D latches with differential clock input

- latch_2ck : D latches with differential clock input, with reset high

- mux2to1 : 2-to-1 muxes

- nand : nand gates

- ndsr : nand-type sr latches

- nor : nor gates

- nsw : nmos switches

- nsw_wovdd : nmos switches without VDD rail

- oai22 : 2-input oai gates

- space : fillers

- space_wovdd : fillers without VDD rail

- tap : tap cells

- tap_wovdd : tap cells without vdd rail

- tgate : transmission gates

- tie : tie cells

- tie_wovdd : tie cells without vdd rail

- tinv : tri-state inverters

- tinv_small : small tri-state inverters

Schematic templates¶

Corresponding schematic templates can be found in: generators/logic/logic_templates.